AgileX M - Premier FPGA Intel AgileX avec mémoire HBM2E et contrôleurs DDR5 et LPDDR5

Ils sont conçus pour la libération du processus technologique de 7 nanomètres Intel

Répondre à une croissance exponentielle des données dans le monde d'aujourd'hui et la transition des clusters informatiques centralisées et des stockages à une architecture plus distribuée, qui "traite partout partout", Intel a introduit les matrices de valve programmables par l'utilisateur (FPGA) de la série AgileX M. Il se caractérise par une grande flexibilité, une efficacité énergétique, une architecture massive parallèle et une vaste bande passante de canaux d'E / S. Ces qualités permettent à FPGA attrayant pour accélérer une large gamme de tâches - du calcul de supercalculateur avant de stocker des données et un métabolisme de réseau.

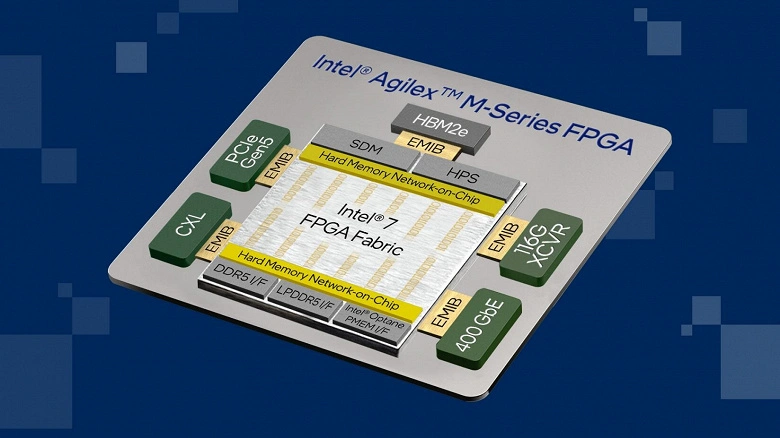

Selon Intel, les nouveaux FPGA ont le débit maximum entre ces produits. Ils ont un DSP avec la plus grande "densité informatique", c'est-à-dire le rapport de la productivité à la zone cristalline. En outre, il s'agit de la première FPGA de la famille Intel AgileX, dans laquelle les contrôleurs de mémoire de mémoire HBM2E et DDR4, DDR5 et LPDDR5 sont intégrés. Les avantages de FPGA AGIILEX M comprennent la prise en charge des taux de transmission maximale, des interfaces PCIe Gen5, de Compute Express Link, de 400g Ethernet et des émetteurs-récepteurs consécutifs fonctionnant à des vitesses allant jusqu'à 116 Go / s.

Il reste à ajouter que ceux-ci sont la première FPGA, conçue pour la libération du processus de 7 nanomètres Intel.